SAN JOSE, CA, May 12, 2025 – Cadence has joined the Autonomous Vehicle Computing Consortium (AVCC), expanding its role in shaping the computing and safety infrastructure behind future autonomous vehicle platforms. By contributing to AVCC’s technical working groups, Cadence will help define high-performance computing architectures that support the growing demands of physical AI in mobility systems. The collaboration supports industry efforts to standardize compute solutions for advanced driver-assistance and autonomous driving applications – an area where performance, power, and safety align by design.

By joining the AVCC, Cadence will help define high-performance system architectures and safety standards needed for real-time image and vision processing in autonomous vehicles. Cadence’s focus is on supporting safe and efficient system design.

Driving High-Performance Computing and Safety Standards

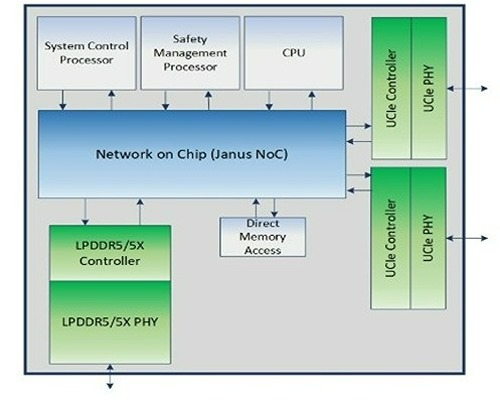

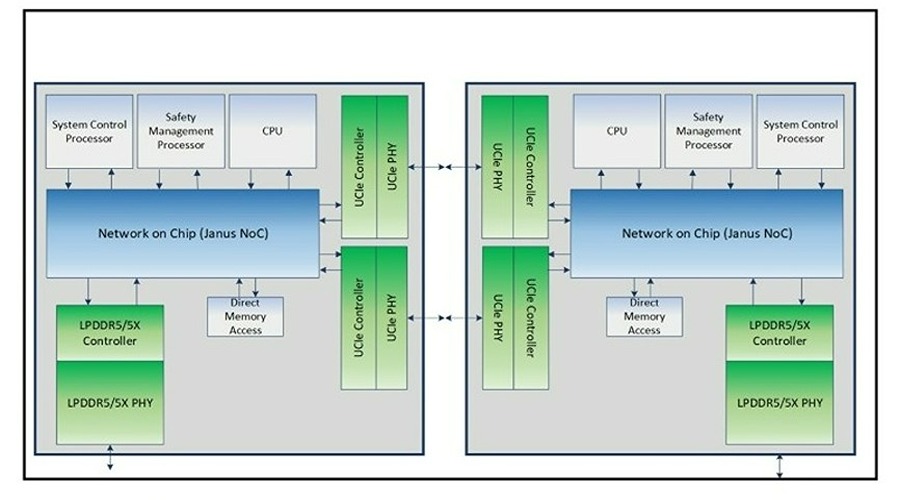

Designing systems on chip (SoCs) for automotive applications involves challenges, particularly as manufacturers rely on chiplets from multiple partners. This approach requires chiplet partitioning to support integration and collaboration across vendors. When product lines are built using a shared set of chiplets, a common partitioning framework becomes essential for reuse and compatibility. The AVCC’s efforts on standardized chiplet partitioning is critical for supporting integration across the automotive ecosystem.

In addition to chiplet partitioning, ensuring interoperability with functional safety is critical in automotive SoC design. As multiple vendors develop SoCs independently using shared chiplets, establishing collaborative safety requirements is essential. This shared approach supports ISO 26262 compliance, ensures integration, and helps standardize semiconductor architectures for automotive automated driver assistance (ADAS) and autonomous vehicles.

Cadence will help set performance and safety benchmarks within the AVCC, focusing on real-time processing, security protocols, and system reliability. These efforts will address issues like cybersecurity risks and fail-safe mechanisms in autonomous vehicles. By supporting interoperable system requirements, Cadence helps develop standards that encourage industry innovation.

Pioneering Innovations with Chiplets

Cadence will also contribute in modular chiplet design to support the consortium’s technical goals. Its chiplet framework enables scalable architectures that can be adapted for different use cases, helping simplify upgrades and customization while controlling development costs. The modular approach also supports secure, high-speed communication between chiplets, ensuring integration while meeting performance and safety needs in autonomous vehicles.

In November 2024, Cadence announced a groundbreaking achievement with the development and successful tapeout of its Arm-based system chiplet, highlighting Cadence’s focus on advancing ADAS, robotics, and drones through its chiplet architecture. Cadence brings this level of innovation to the consortium’s work.

“Cadence is committed to driving the next wave of physical AI innovation in autonomous vehicle technology by addressing key challenges in performance, safety, and interoperability. Our collaboration with the AVCC reinforces our mission to deliver cutting-edge solutions that transform the autonomous driving landscape,” said David Glasco, vice president, research and development, Silicon Solutions Group, Cadence.

“AVCC is thrilled to welcome Cadence as a member,” said Sarah LaLiberte, vice president of AVCC. “Their expertise in high-performance computing, chiplet architectures, and functional safety aligns perfectly with our mission to drive innovation in autonomous vehicle technology. Collaboration is key to solving the industry’s most complex challenges, and Cadence’s leadership in silicon design and system integration will help accelerate the development of scalable, interoperable, and safety-driven solutions for next-generation autonomous systems.”

About Cadence

Cadence Design Systems, Inc. is a U.S.-based technology firm that develops electronic design automation (EDA) tools, hardware, and IP for designing integrated circuits and electronic systems. Formed in 1988 through the merger of SDA Systems and ECAD, the company is headquartered in San Jose, CA. Cadence provides software and solutions for designing SoCs, PCBs, and complete electronic systems used in the semiconductor, automotive, aerospace and defense, telecommunications, and consumer electronics industries. Its tools support both digital and analog design workflows. As of 2024, Cadence reported annual revenue of approximately $4.64 billion and employed about 12,703 people globally. The company’s technology support the design, verification, and optimization of complex electronics across various industries.

About Autonomous Vehicle Computing Consortium (AVCC)

The Autonomous Vehicle Computing Consortium (AVCC) is a nonprofit industry group established in 2019 to define computing requirements for automated and autonomous vehicles. It brings together companies from the automotive, semiconductor, and software sectors to collaborate on standardizing compute platform architectures that support functions such as perception, decision-making, and control. AVCC focuses on balancing performance, power consumption, and safety in its technical guidelines, with the goal of making systems scalable to integrate across different vehicle platforms. The consortium serves the automotive and mobility industries, supporting the development of both advanced driver-assistance systems (ADAS) and fully autonomous solutions. AVCC is supported by its members and functions as a collaborative industry body. AVCC is headquartered in San Jose, CA, and serves as a platform for aligning technical needs in autonomous vehicle development.