SAN JOSE, CA, May 9, 2025 – NEO Semiconductor has expanded its 3D X-DRAM portfolio with 1T1C and 3T0C cell architectures, aiming to enhance DRAM scalability, power efficiency, and memory density. These innovations are designed to support high-performance computing, AI workloads, and data-centric applications by addressing limitations of traditional DRAM in modern, scalable memory systems.

NEO Semiconductor’s 1T1C and 3T0C 3D X-DRAM designs use a 3D NAND-like architecture to support DRAM functionality with improved manufacturing efficiency. Proof-of-concept chips are expected in 2026, with target densities up to 512Gb for applications in AI, edge computing, and data processing.

“With the introduction of the 1T1C and 3T0C 3D X-DRAM, we are redefining what’s possible in memory technology,” said Andy Hsu, founder & CEO of NEO Semiconductor. “This innovation pushes past the scaling limitations of today’s DRAM and positions NEO as a frontrunner in next-generation memory.”

Key Features and Benefits:

- Unmatched Retention and Efficiency – Thanks to IGZO channel technology, 1T1C and 3T0C cell simulations demonstrate retention times of up to 450 seconds, reducing refresh power.

- Verified by Simulation – TCAD (Technology Computer-Aided Design) simulations confirm 10-nanosecond read/write speeds and over 450-second retention time.

- Manufacturing-Friendly – Uses a modified 3D NAND process, with minimal changes, enabling full scalability and integration into existing DRAM manufacturing lines.

- Ultra-High Bandwidth – Employs array architectures for hybrid bonding to enhance memory bandwidth and reducing power consumption.

- High Performance for Advanced Workloads – Designed for AI, edge computing, and in-memory processing, with high-speed access and reduced energy consumption.

Expanding the 3D X-DRAM Family:

NEO Semiconductor’s technology platform includes three 3D X-DRAM variants:

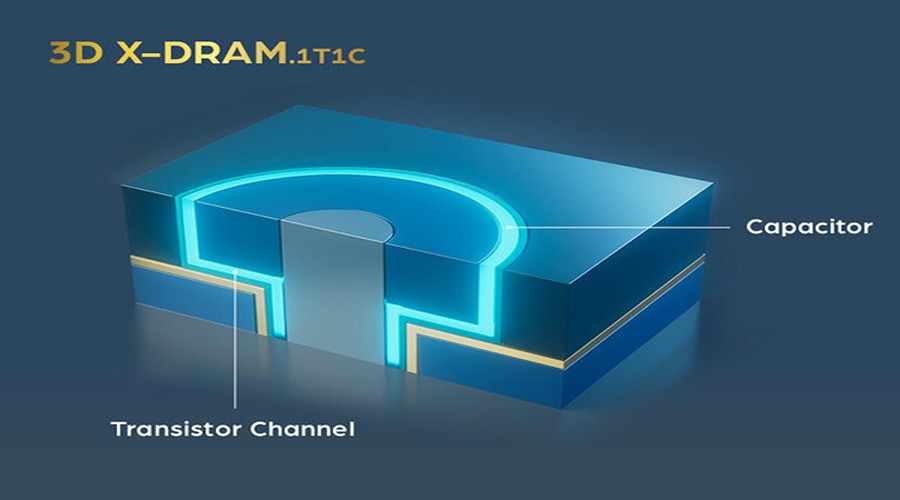

- 1T1C (one transistor, one capacitor) – The core solution for high-density DRAM, compatible with mainstream DRAM and HBM roadmaps.

- 3T0C (three transistor, zero capacitor) – Optimized for current-sensing operations, suitable for AI and in-memory computing.

- 1T0C (one transistor, zero capacitor) – A floating-body cell structure suitable for high-density DRAM, in-memory computing, hybrid memory and logic architectures.

Source: NEO Semiconductor

About NEO Semiconductor

NEO Semiconductor, founded in 2012 and based in San Jose, California, is a fabless semiconductor company specializing in advanced memory technologies. The company focuses on developing next-generation solutions in 3D NAND flash, 3D DRAM, and 3D AI chip architectures, targeting performance and scalability for data-intensive applications. Its flagship innovation, X-NAND, combines SLC-level speed with the cost-efficiency of TLC and QLC memory, making it suitable for AI, 5G, and other high-bandwidth environments. In 2023, NEO introduced 3D X-DRAM, the industry’s first DRAM built using a 3D NAND-like cell structure to address the scaling limitations of traditional DRAM. Most recently, in 2024, the company launched 3D X-AI, an architecture aimed at enhancing AI processing capabilities with improved power efficiency. NEO holds more than 30 U.S. patents across memory architecture and cell design. The company’s innovations continue to serve industries such as AI, edge computing, and data centers.