TOKYO, Japan and SAN FRANCISCO, CA, Feb 19, 2026 – Renesas Electronics has introduced a configurable ternary content-addressable memory (TCAM) built on a 3nm FinFET process. The TCAM targets higher density, lower power consumption and improved functional safety for automotive applications. Renesas presented the design results at the International Solid-State Circuits Conference 2026, held Feb 15–19 in San Francisco.

Network traffic is increasing as 5G and cloud and edge computing expand, raising demand for larger TCAM arrays such as 256-bit × 4,096 entries. Conventional scaling that relies on hard macros expands peripheral circuitry, adds banks and repeaters, complicates timing closure and increases search power. Automotive applications also require safety coverage to comply with ISO 26262.

Integrated Hard- and Soft-Macro Approach for Flexible Configuration

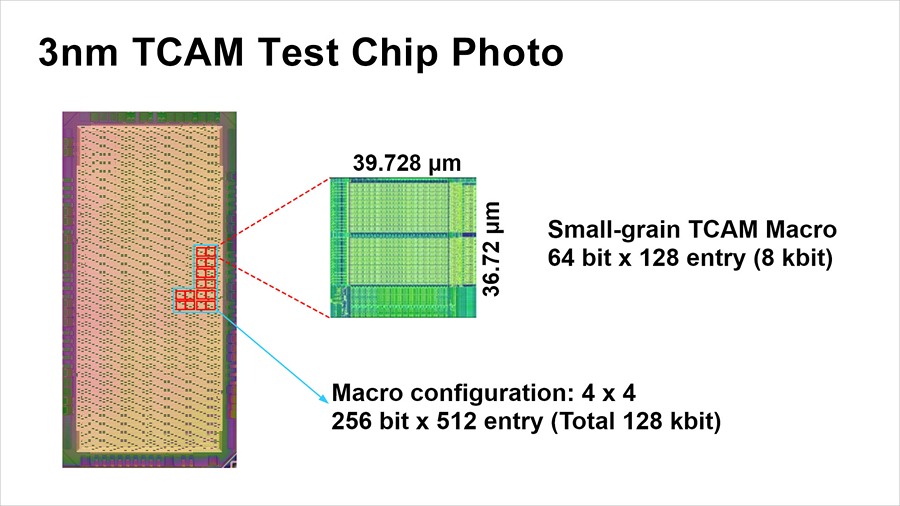

A memory compiler supports the TCAM hard macros with search key widths of 8–64 bits and entry depths of 32–128 bits. Designers can scale to larger arrays (e.g., 256-bit × 4,096 entries) by combining hard macros with tool-driven soft-macro auto-generation. This method creates a configurable single macro and achieves a memory density of 5.27 Mb/mm².

All-mismatch Detection and Macro-Level Pipelined Search

Each TCAM hard macro integrates an all-mismatch detection circuit1 and uses a two-stage pipelined search. The second stage runs only when the first stage detects a potential match. If no match is found, the process stops to avoid additional energy use. For example, in 64–256-bit × 512-entry configurations, the approach reduces search energy by:

- Up to 71.1% with column-wise pipelined search (with key partitioning, >64-bit keys)

- Up to 65.3% with row-wise pipelined search (without key partitioning, ≤64-bit keys)

In a 256-bit × 512-entry configuration, the design achieves low-power operation with search energy of 0.167 fJ/bit, and the distributed timing load enables a 1.7 GHz search clock. The resulting TCAM figure-of-merit (density × speed ÷ energy) reaches 53.8, exceeding prior work.

Enhanced Functional Safety for Automotive Applications (Split Data Bus and Dedicated SRAM)

TCAM bitcells at the same address are physically adjacent, so a double-bit soft error cannot be corrected by conventional SECDED ECC2. Renesas abates this with two techniques:

- Separates odd/even data paths for user data and ECC parity to increase cell spacing, turning potential double-bit errors into correctable single-bit errors.

- Uses a separate SRAM for ECC parity with its own address decoder to improve error detection during TCAM write operations.

The added error mitigation techniques increase safety coverage for automotive use. Configurable key widths and entry depths allow the TCAM to scale across system requirements. Lower power operation and functional safety support deployment in automotive, industrial and consumer devices that manage data exchange between sensors and processors. Renesas said it will continue refining memory architectures focused on capacity, power efficiency and reliability.

1All-mismatch detection: A circuit that determines in the first search stage whether all entries are mismatches and controls whether the second stage is executed.

2SECDED (Single Error Correction, Double Error Detection): An ECC scheme that corrects single-bit errors and detects double-bit errors.

Source: Renesas Electronics

About Renesas Electronics

Renesas Electronics, based in Tokyo, supplies power management integrated circuits (PMICs) and ships more than 1.5 billion power devices annually for computing, industrial, IoT, data center, and communications markets. Its portfolio includes PMICs, discrete devices, GaN power products, and design tools such as PowerCompass and PowerNavigator. These work with microcontrollers, SoCs, and connectivity solutions to support system design. The company was formed in 2010 through the merger of Renesas Technology and NEC Electronics, with origins in semiconductor units of Hitachi, Mitsubishi, and NEC.